(Multidisciplinary Open Access Refereed e-Journal)

### Design of Serial and Mixed Mode Flip Flop Scan Test with High Performance

<sup>1</sup>T.Raja, <sup>2</sup>M.Nisha, <sup>3</sup>R.Sangeetha, <sup>4</sup>M.Sowndarya, <sup>5</sup>G.Sri Loga

<sup>1</sup>Assistant Professor, <sup>2,3,4,5</sup>UG Students – Final Year, Department of Electronics and Communication Engineering, Vivekanandha College of Technology for Women, Namakkal, Tamilnadu, India

## Abstract

The capacity of sequential sweep configuration has been the standard technique for assessing VLSI (Very Large-Scale Integration Circuits) before. Sequential output plan has turned into the non-self-plan for testability techniques over the strategy. Since it is easy to develop, the sequential sweep configuration has ruled the test design. In sequential output plan, the current sweep cell stays away from the weaknesses of earlier output cells, for example, the defer brought about by the output multiplexers connected to each flip-inputs. Flop the sequential output design, then again, produces inordinate exchanging action during testing, bringing about superfluously high power dispersal. The current sweep cell configuration is utilized as a typical output flip-flop in the "blended check" test, which permits it to work as both a sequential and a Random Access Scan (RAS) cell. In this technique, another blended mode filter plan design is suggested that consolidates sequential and arbitrary activities in a solitary module, bringing about changes in RAS cells where sequential information correspondence is inside associated with check cells in series, permitting information to be gotten in both sequential and irregular strategies from each output cell. When contrasted with the present blended mode check plan, it further develops exchanging movement and diminishes power utilization. The exploratory outcomes show that general region, power utilization, and inactivity may be in every way diminished.

### 1. Introduction

VLSI processors' power utilization has been consistently developing. In elite execution computerized frameworks, low-power configuration is turning out to be progressively significant. With regards to planning low-power VLSI circuits, there are a ton of choices. Low power has accentuated the significance of force scattering with regards to execution and space. Shopper opinions about approach and progress toward portability are positive. Their need originates from a developing interest for minimal applications with high throughput and low power utilization. Note pad and versatile PCs, for instance, presently have tantamount processing ability as working Systems. Different AI sorts of rationale circuits increment the presentation of a hardware framework as CMOS innovation advances towards the nanometer scale. Since a few boundaries are impacted as gadgets are downsized, using various sorts of rationale circuits to build the exhibition of a hardware framework. Successive rationale circuits are one of the main types of rationale circuits that are fundamental for the development of any kind of electronic framework. The main fundamental structure components of Very Large Scale Integrated Circuits are D Flip Flops (DFF) (VLSI).

These designs might be named static or dynamic, with dynamic DFFs beating static DFFs as far as Power Delay Product (PDP). D flip failures are utilized in low-power Analog to Digital Converters (ADCs) in unmistakable squares of Multichannel ADCs for PET scanners. While utilizing a MHz recurrence range, a static D flip-flop is fairly languid, henceforth a TSPC D-flip-flop is utilized to forestall this. Nonetheless, there are different defects in the go-between hubs, making the circuit's general exhibition endure. For multi-bit back-peddles, clock power decrease is an especially proficient arrangement.

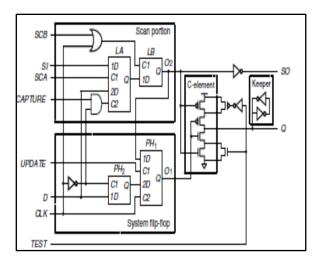

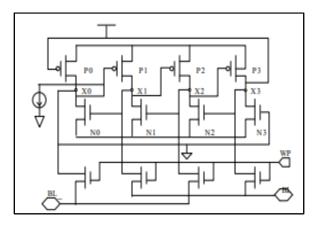

Figure.1 Error Correcting Scan Flip-flop Design

By consolidating a couple of flip failures with various piece goes back and forth, unnecessary inverters might be eliminated. These multi-bit back-peddles may share drive strength, dynamic power, and inverter chain region, and even diminish clock network power and make slant the board more straightforward. To start with, simultaneous clock signals are used to recognize goes back and forth that might be converged; next, a blend table is created to indicate the likely mixes of flip-flops; and ultimately, a progressive strategy is utilized to consolidate back-peddles. A special heartbeat set off Flip-Flop (FF) engineering with decreased power utilization to advance a faster release activity, the beat age control rationale, an AND work, is taken out from the basic way. To diminish intricacy, an essential twosemiconductor and entryway configuration circuit is utilized. Second, a restrictive heartbeat development approach just plans for the essential pathway to accelerate release because of the interest. Therefore, the size of the semiconductors in the defer inverter and heartbeat creation circuit might be brought down to save power. By disposing of the output multiplexer from the useful course, it diminishes the sequential sweep's exhibition cost. In a blended mode check test, it could be utilized as a sequential output cell as well as a RAS cell. The proposed idea utilizes the test control signal as a semi consecutive or low-recurrence examine clock as opposed to adding a control signal. The new output flip-lemon can play out every one of the tests that a conventional sweep flip-failure can do.

(Multidisciplinary Open Access Refereed e-Journal)

### 2. Related Works

In the current strategy, Serial output testing involves going information through examine chains in a successive way, which is proficient yet has a few disadvantages. The volume of test information Time to test the application. Power utilization to test the presentation upward is because of filtering multiplexers, which is one of the weaknesses. These output multiplexers add two doors of postponement, which pumps the brakes significantly more. The basic way between two flip-lemon can use to work out the defer that influences the plan. Subsequently, the very trick multiplexers that create setback impacts in plan are utilized for filter addition in testing. Furthermore, this increments yield fan-out. This dials back testing by presenting a more basic way delay, which decreases utilitarian clock speed by 5% to 10%. The multiplexer at the contribution of the expert hook chooses between Functional Input (D) and Scan Input (SI) contingent on the worth of test control signal test Enable (TE). In test mode, when TE is high (1), SI is chosen and is associated with the expert lock's feedback. Whenever the Clock Signal (CP) is low (0), the worth of SI spreads to the expert lock. In the in the interim, the slave hook holds the worth from the past clock cycle. The worth hooked into the expert proliferates to the slave lock when CP goes to high (1), and the result Q of output flip-flop. Sequential output plan has turned into the accepted testability plan technique. On account of the straightforwardness of testing and superb test inclusion, has without a doubt acquired critical industry acknowledgment. Nonetheless, there are disadvantages to the sequential sweep engineering. Execution weakening, test information volume, test application time, and test power squander are among the punishments. The sweep multiplexers connected to the contributions of each flip-flop add to the presentation upward of output plan.

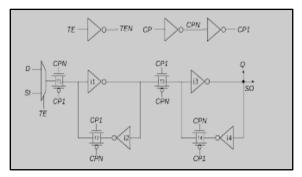

Figure.2 Latch structure of 12 tube DICE

The presentation crumbling brought about by the sweep multiplexer has become enhanced in the present extremely high velocity gadgets with the littlest accessible combinational profundity. Thus, the fleeting upward of output plan should be addressed to protect circuit execution. An original output flip-flop design is recommended that evades the

(Multidisciplinary Open Access Refereed e-Journal)

exhibition upward of sequential sweeps. By successively applying the clock signal, all flip-flops in the sweep chain are stacked with the fitting information.

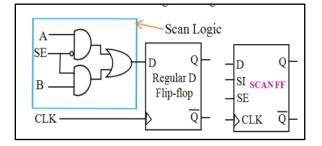

Figure.3 Progressive Random Access Scan Cell

The successive test issue is diminished to a combinational test issue by utilizing a total output plan. One of the most troublesome challenges in the plan of nanoscale coordinated circuits in aeronautical gear is radiation. Aviation chips should be constructed utilizing radiation-safe standard cell libraries. The Design for Testability (DFT) approach, which depends on a particular cell library, is a method for further developing unwavering quality in the chip configuration process, and the examining D flip-flop is the fundamental unit vital for testability plan. On the radiation-safe chip's DFT, the radiation-solidified examine D flip-flops are made and affirmed from the circuit and format levels to resolve the issue of no filtering D flip-flops in the radiation-safe standard cell library of SMIC 0.18um. As per the reenactment discoveries, the radiation-solidified checking D flip-flop has a reliable radiation opposition. Quantum-Dot Cellular Automata (QCA) Technology is an arising trade for CMOS innovation in the development of advanced circuits. Future nanoscale advanced circuits in light of QCA innovation will be very good with regards to control utilization, gadget thickness, and speed.

Figure.4 Scan Flip-flop Design For Serial

Larger part Gate (MG) and Inverter are the standard rationale parts of Cellular Automation. This is a 5-input MG rationale circuit. The multiplexer MG has different

(Multidisciplinary Open Access Refereed e-Journal)

disadvantages, most outstandingly the need for additional entryways to make convoluted capacities. The 5-input MG is utilized to make undeniable level amalgamation circuits like multiplexers, shift registers, and output Flip-flops.

Figure.5 Scan Logic Inputs in SFF and it's block diagram

CMOS innovation is a fast innovation that is approaching its scaling limits. In any case, CMOS innovation has a few blemishes. QCA can wipe out the disadvantages of CMOS at the nanoscale. OCA circuits are comprised of basic components known as OCA cells, which are comprised of two movable electrons. As a result of their coulombic energy, these electrons are continually involved at the contradicting inclining corners. The electrons' positions bring about two likely polarizations. The larger part doors and the 2:1 multiplexer (mux) are the main parts of the consistent framework. Thus, the rationale parts in the 2:1 mux structure are decreased. Quantum-Dot Cellular Automata (QCA) Technology is an arising trade for CMOS innovation in the development of advanced circuits. Future nanoscale advanced circuits in light of QCA innovation will be very good with regards to control utilization, gadget thickness, and speed. Larger part Gate (MG) and Inverter are the standard rationale parts of Cellular Automation. This is a 5-input MG rationale circuit. The multiplexer MG has different disadvantages, most outstandingly the need for additional entryways to make convoluted capacities. The 5-input MG is utilized to make undeniable level amalgamation circuits like multiplexers, shift registers, and output Flip-flops. When contrasted with before circuits worked with 3-input MG, the recommended circuits have benefits as far as many circuit measurements, for example, cell counts, region, and door count.

## 3. Proposed Method

The sweep multiplexers added to each flip sources of info flops add to the output plan's presentation upward. The presentation debasement brought about by check multiplexers has become amplified in the present extremely fast plans with the littlest conceivable combinational profundity. The new sweep flip-flop plan in this technique

(Multidisciplinary Open Access Refereed e-Journal)

disposes of the sequential output's exhibition upward. The output multiplexer is taken out from the utilitarian way in the proposed plan.

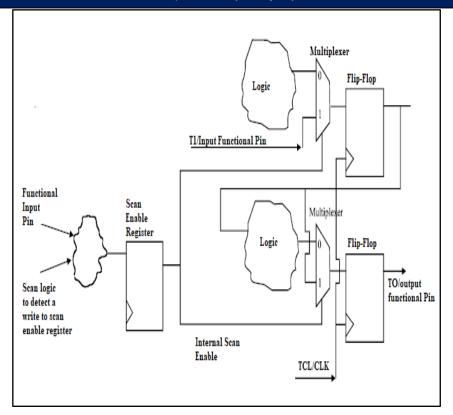

The proposed plan can possibly work on the practical recurrence of execution basic plans. Therefore, the sweep configuration's timing upward should be addressed to keep up with circuit execution. Moreover, in a "blended check" test, the proposed plan can be utilized as a sequential sweep cell as well as a typical output flip-flop. The output chain engineering plan with proficient execution boundaries regarding region and deferral in this proposed work.

# 3.1 Functional Mode

The carrying out plan utilizes just a single sort of sweep cell called Random Access Scan Cells (RAS), which can be utilized for both sequential and irregular output tasks, though the current strategy utilizes two kinds of output cells, one for a considerable length of time checks and the other for arbitrary access filter tests, which occupies more room and time. They consolidate sequential and arbitrary tasks in a solitary module, the RAS cell, which has sequential information correspondence inside with series, examine cell associations and gets information in both a sequential and irregular way from each output cell.

# Figure.6 Proposed block diagram

(Multidisciplinary Open Access Refereed e-Journal)

### 3.2 Random Accesses Scan

Carrying out a sweep chain engineering plan with effective execution standards regarding region and time in this recommended work. The executing configuration utilizes just a single sort of sweep cell called irregular access examine cells, which can be utilized for both sequential and arbitrary output tasks, while the current procedure utilizes two kinds of output cells, one for a very long time checks and the other for arbitrary access filter tests, which occupies more room and time. To join sequential and irregular activities in a solitary module, we utilize a RAS cell, which has sequential information correspondence inside with series filter cell associations and gets information in both a sequential and arbitrary way from each output cell.

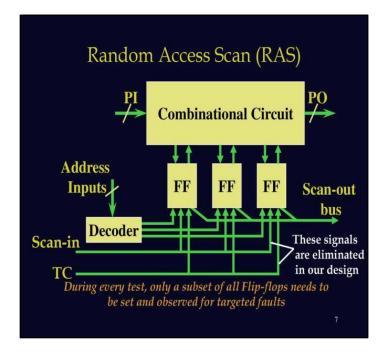

Figure.7 Functional Architecture of RAS Flip-flop

The advancement of VLSI innovation, which came about in a consistently expanding number of semiconductors in a solitary chip, made them incredibly hard to test. It is difficult to get astounding issue inclusion without involving Design for Testability (DFT) strategies since the capacity parts are less controllable and recognizable. It is more straightforward to test muddled plans utilizing DFT techniques. Specially appointed DFT strategies and underlying DFT techniques are the two kinds of DFT techniques utilized in this system. These Ad-hoc DFTs have specific constraints, for example, the failure to make high issue inclusion and the powerlessness to deal with high-intricacy plans. Specially appointed DFT techniques.

(Multidisciplinary Open Access Refereed e-Journal)

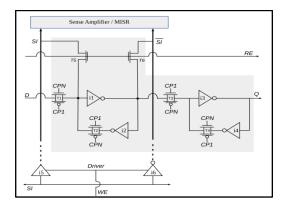

Check configuration is especially huge in this plan cycle, and it assumes a basic part in testing advanced circuits by improving controllability and discernibleness.

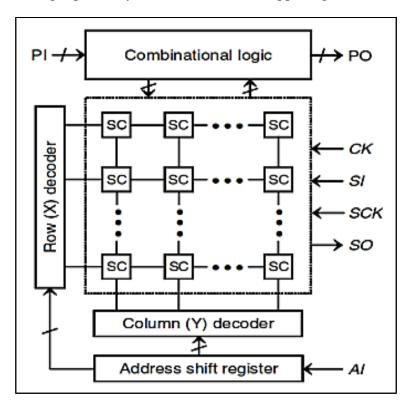

Examine cells are organized in a two-layered exhibit that might be gotten to in any request for perception (perusing) or refreshing (composing). This total arbitrary access capacity is given by utilizing a line (X) and segment (Y) decoder to unravel an entire location. The sweep cell to be gotten still up in the air by a log2nbit address shift register. The state vector may now be recovered in an arbitrary grouping, which recognizes this method from prior ones. The test application time can be brought down since encompassing examples can be arranged with the goal that they vary in only a couple of pieces and a couple of reaction bits should be observed. The length of the test is sliced down the middle with this technique. This technique permits you to 'watch' what's happening.

Figure.8 Random Access Scan Design

An exceptional kind of output flip-flop with an extra hook intended for low power testing applications. The control input HOLD keeps the result consistent at the past condition of the flip-flop. For HOLD = 0, the hook holds its state and for HOLD = 1, the hold lock becomes straightforward. For ordinary mode activity, TC = HOLD = 1 and for check mode, TC = 1 and Hold = 0. Equipment upward increments by around 30% because of additional

(Multidisciplinary Open Access Refereed e-Journal)

equipment in the hold lock. This approach decreases power dissemination and secludes offbeat parts during the sweep, it is appropriate for defer tests.

In a Random-Access filter plan, a part of the flip-flops is used to approach successive result and the other flip-flops structure RAS design. Both consecutive output test designing and RAS test configuration are worked at the same time. Be that as it may, here the halfway mode working of sweep chains is likewise supplanted and worked with RAS cells. The successive sweep chain is executed for sequential information move in blended mode. The flip-flounders that are integrated into RAS design are replaced by RAS cells. The clock ought to be in a dormant state for the whole effort. Consequently, the successive result part can't be worked at the same time with RAS using the conventional consecutive sweep cell. The proposed yield cell overcomes this issue by using test control movement as a moderate recurrence channel clock and allows work of both successive and RAS arrangement in equal.

# 3.3 Software Description

Xilinx is revealing this Document and Intellectual Property (from here on out "the Design") to you for use in the advancement of plans to work on or connect with Xilinx FPGAs. Besides as expressed thus, none of the plan might be duplicated, imitated, disseminated, republished, downloaded, showed, posted, or communicated in any structure or using any and all means including, yet not restricted to, electronic, mechanical, copying, recording, or in any case, without the earlier composed assent of Xilinx. Any unapproved utilization of the plan might disregard intellectual property regulations, brand name regulations, the laws of protection and exposure, and correspondences guidelines and resolutions. Xilinx accepts no obligation emerging out of the application or utilization of the plan, nor does Xilinx convey any permit under its licenses, copyrights, or any privileges of others. You are liable for acquiring any freedoms you might expect for your utilization or execution of the plan. Xilinx claims all authority to make changes, whenever, to the plan as considered alluring at the sole tact of Xilinx. Xilinx accepts no commitment to address any blunders contained thus or to inform you regarding any adjustment assuming such be made. Xilinx won't expect any responsibility for the precision or accuracy of any designing or specialized help or help furnished to you regarding the plan.

## 3.4 HDL-Based Design

This section guides you through a run of the mill HDL-based plan technique utilizing the plan of a sprinter's stopwatch. The plan model utilized in this instructional exercise shows numerous gadget highlights, programming elements, and configuration stream rehearses you can apply to your plan. This plan focuses on a Spartan<sup>TM</sup>-3A gadget; nonetheless, the standards as a whole and streams instructed apply to any Xilinx® gadget family except if generally noted. The plan is made out of HDL components and two centers. You can blend the plan utilizing Xilinx Synthesis Technology (XST), Simplify/Simplify Pro, or Precision. This part is the primary section in the "HDL Design Flow."

(Multidisciplinary Open Access Refereed e-Journal)

After the plan is effectively characterized, you will perform conduct reenactment ("Behavioral Simulation"), run execution with the Xilinx Implementation Tools ("Design Implementation"), perform timing recreation ("Timing Simulation"), and arrange and download to the Spartan-3A demo board ("IMPACT Tutorial"). To play out this instructional exercise, you should have the accompanying programming and programming parts introduced:

Xilinx Series ISE<sup>™</sup> 9.1i.

Simple 3A libraries and gadget documents.

This instructional exercise accepts that the product is introduced in the default area c:\xilinx91i. Assuming you have introduced the product in an alternate area, substitute your establishment way for c:\xilinx91i in the accompanying strategies.

# 4. Conclusion

The new blended mode examine plan engineering utilizes a RAS (Random Accesses Scan) plan to get to information successively and arbitrarily, wiping out the presentation cost of the past blended mode check plan design. When contrasted with the present blended mode filter plan, it further develops execution regarding exchanging action and power utilization. By eliminating the sweep multiplexer from the practical way, the output flip-flop engineering dodges the presentation punishment of sequential examining. The new sweep flip-flop is fit for playing out every single standard test and is planned and tried observing industry guidelines. In the blended mode check test, the recommended filter flip-failure can be utilized as a sequential output cell as well as a RAS cell. The recommended check flip-flop shows guarantee in lessening interconnect wire length, test information volume, and test application time in a blended mode filter framework.

## References

- 1. Ahlawat, S., Tudu, J., Matrosova, An and Singh, V. "A superior presentation check flip-flop plan for sequential and blended mode examine test". IEEE Transactions on Device and Materials Reliability, 18(2), 321-331. 2018

- Li, M., Cao, B., Lai, F., and Zhang, N. "Plan and check of radiation-solidified filtering D Flip-Flop". IEEE third International Conference on Electronics Technology (ICET). 2020.

- 3. Ajitha, D., Ahmed, S., Ahmad, F., and Rajini, G. K. "Plan of region productive shift register and output flip-flop founded on QCA innovation". Global Conference on Emerging Smart Computing and Informatics (ESCI). 2021.

- 4. G. R. Somanathan, R. Bhakthavathchalu and K. M, "Adjusted check tie examination to further develop issue inclusion in VLSI circuits", International Conference on Inventive Computation Technologies (ICICT), pp. 307-311, 2021.

- 5. G. R. Somanathan, R. Bhakthavathchalu and K. M, "Adjusted examine fasten investigation to further develop issue inclusion in VLSI circuits", International Conference on Inventive Computation Technologies (ICICT), pp. 307-311, 2021.

- M. Kanda, M. Hashizume, F. A. Binti Ali, H. Yotsuyanagi and S. Lu, "Open imperfection discovery not using limit filter back-peddles in collected circuit sheets", IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 10, no. 5, pp. 895-907, May 2020.

- 7. Q. Wang and L. Jin, "A radiation-solidified examine flip-flop plan with worked in delicate blunder strength", twelfth IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2014,

- 8. K. Suhag and V. Shrivastava, "Postpone testable improved check flip-flop: DFT for high issue inclusion", International Symposium on Electronic System Design, pp. 129-133, 2011.

- 9. Y. Tsiatouhas, A. Arapoyanni, and D. Skias, "An output flip-flop for low-power check activity", fourteenth IEEE International Conference on Electronics, Circuits, and Systems, pp. 439-442, 2007

- K. Eedupuganti and N. S. Murty, "Elite execution and power-mindful output flip-flop plan", IEEE International Conference on Computational Intelligence and Computing Research (ICCIC), pp. 1-4, 2017.